我院黄智恒副教授在三维微电子封装铜硅通孔凸起机理原子尺度研究取得进展

三维微电子封装热管理因素尤为突出,其原因是封装材料特征尺寸已缩小至几个微米,原位实验表征困难,材料微观结构因素包括原子尺度结构对封装材料的热管理和可靠性设计造成挑战。传统电子封装可靠性模拟与仿真结果与实验不符,领域急需面向三维微电子集成与封装可靠性模拟与仿真的新方法和新工具。我院黄智恒副教授研究小组在三维微电子封装铜硅通孔凸起机理原子尺度研究中取得进展,相关研究成果近日以专著章节的形式呈现在Springer先进微电子系列第64卷《三维微电子封装:从架构到应用》(3D Microelectronic Packaging: From Architectures to Applications)一书(Springer Link:https://link.springer.com/book/10.1007%2F978-981-15-7090-2)中,该书由英特尔工程师主编,共18个章节,章节通讯作者来自英特尔、美国华盛顿州立大学、美国加州大学洛杉矶分校、美国Sandia国家实验室、日本东京大学等企业、高校和科研机构。

该书中我院黄智恒副教授参与贡献四个章节,也是其中两个章节的通讯作者,材料科学与工程学院2017级学术型硕士生刘金欣(2020年6月已毕业)是该书中两个章节的第一作者。该书第一版《三维微电子封装:从基础到应用》(Springer Link:https://link.springer.com/book/10.1007%2F978-3-319-44586-1)2017年出版后获得领域内好评,此次出版的是该书第二版。第二版中的第5章和第6章详细报道了使用相场晶体法研究铜硅通孔原子尺度行为以及造成硅通孔凸起的原子尺度机理。

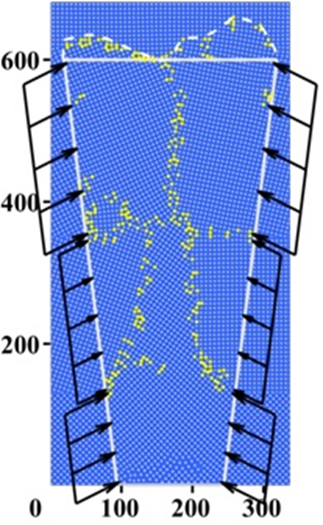

铜硅通孔(Cu-TSV)凸起过程的相场晶体(PFC)法原子尺度仿真

该项研究工作跨度五年多,相关研究结果发表在 IEEE Journal of the Electron Devices Society (Vol. 7: 1270-1276, 2019)、ASME Journal of Electronic Packaging (Vol. 142: 011009-1-9, 2020 )等杂志,研究进展曾在IEEE ESTC 2016(欧洲电子系统集成技术会议),ICEPT 2017(国际电子封装技术会议),EMAP 2018(国际电子材料与封装国际会议),EDTM 2019(第3届电子器件技术和制造会议)等国际会议上作展示,并曾获2017年ICEPT最佳学生论文一等奖。该项研究相关内容2012-2015年获得广州市珠江科技新星“三维电子封装集成计算材料工程”专项资助,2015-2020获得广东省自然科学基金研究团队项目(批准号:2015A030312011)资助。